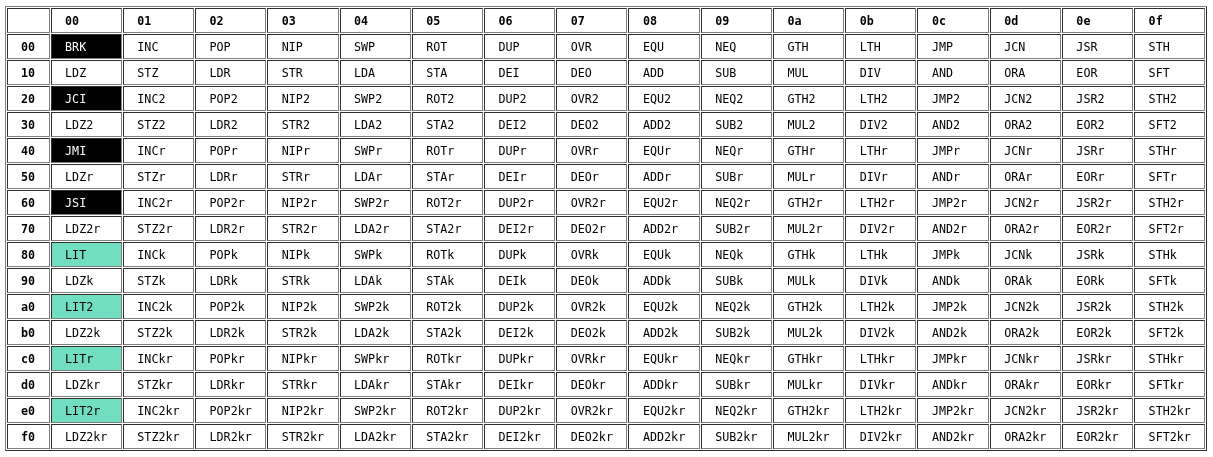

Uxntal Opcodes

Uxn has 32 standard opcodes and 4 immediate opcodes. In the table below, the pipe(|) character

indicates an effect on the return stack, the pc is the program counter, a value8 indicates a byte

length, a value* indicates a short length, an unspecified length follows the short mode and a [value] is read from memory.

Stack I Logic Memory I Arithmetic BRK -- EQU a b -- a=b LDZ abs8 -- [abs8] ADD a b -- a+b INC a -- a+1 NEQ a b -- a≠b STZ val abs8 -- SUB a b -- a-b POP a -- GTH a b -- a>b LDR rel8 -- [rel8] MUL a b -- a×b NIP a b -- b LTH a b -- a<b STR val rel8 -- DIV a b -- a÷b Stack II Stash Memory II Bitwise SWP a b -- b a JMP addr -- LDA abs* -- [abs*] AND a b -- a&b ROT a b c -- b c a JCN cond8 addr -- STA val abs* -- ORA a b -- a|b DUP a -- a a JSR addr -- | pc* DEI dev -- [dev] EOR a b -- a^b OVR a b -- a b a STH a -- | a DEO val dev -- SFT a sft8 -- res LIT -- [pc*] JCI cond8 -- JMI -- JSI -- | pc*

Modes

An opcode is any name in which the 3 first characters are found in the opcode table, followed by any combination of 2, k and r. Each opcode has 3 possible modes, which can combined:

- The short mode 2 operates on shorts, instead of bytes.

- The keep mode k operates without consuming items.

- The return mode r operates on the return stack.

| INC2r | |||||||

|---|---|---|---|---|---|---|---|

| k | r | 2 | opcode | ||||

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

By default, operators consume bytes from the working stack, notice how in the

following example only the last two bytes #45 and #67

are added, even if there are two shorts on the stack.

#1234 #4567 ADD12 34 ac

The short mode consumes two bytes from the stack. In the case of jump opcodes, the short-mode operation jumps to an absolute address in memory. For the memory accessing opcodes, the short mode operation indicates the size of the data to read and write.

#1234 #4567 ADD2 57 9b

The keep mode does not consume items from the stack, and pushes the result on top. Every opcode begins by popping values from the stack before operating on them. This mode keeps a copy of the stack pointer to recover after the popping stage.

#1234 #4567 ADD2k 12 34 45 67 57 9b

The return mode swaps the stacks on which an opcode

operates. Under this mode, a return address will be pushed to the working

stack, and stashing will take from the return stack. For that reason, there is

no return opcode. For example, the JSR opcode pushes the

return address onto the return stack, and JMP2r jumps to that

address.

LITr 12 #34 STH ADDr STHr 46

Immediate opcodes

Immediate opcodes are operators that do not take items from the stack, but read values stored immediately after the opcode in the program's memory. Uxntal has 4 immediate opcodes:

- The literal LIT opcode, also written as #.

- The jump !routine.

- The conditional jump ?routine.

- The subroutine routine.

The immediate jump opcodes are slightly faster than their standard opcode counterparts, but do not have modes and cannot be used to do pointer arithmetic. The address value of the immediate opcodes are stored in memory as relative shorts, enabling routines making use of these opcodes to be moved around in the program's memory.

@on-reset ( -> )

#0007 fac-rec BRK

@fac-rec ( n* -- res* )

#0001 GTH2k ?{ NIP2 JMP2r }

OVR2 SWP2 SUB2 fac-rec MUL2 JMP2r

| INC2r | |||||||

|---|---|---|---|---|---|---|---|

| k | r | 2 | opcode | ||||

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

This documentation includes hand gestures, and glyphs, which might serve a dual purpose; both enabling the usage of Uxntal outside of the computer, as well as to help students to familiarize themselves with hexadecimal finger-counting and bitwise operations.

- In the a b -- c d notation, "a b" represent the state of the stack before the operation, "c d" represent the state after the operation, with "b" and "d" on top of the stack, respectively.

- The PC, or program counter, is the location in memory right after the reading of an opcode. Immediate opcodes will have an offset equal to the length of the data stored immediately after the opcode.

Break

.png)

BRK -- Ends the evalutation of the current vector. This opcode has no modes.

Jump Conditional Immediate

JCI cond8 -- Pops a byte from the working stack and if it is not zero, moves the PC to a relative address at a distance equal to the next short in memory, otherwise moves PC+2. This opcode has no modes, it is written using the ?label format.

#0a DUP ?label INC @label ( 0a )

#0a #01 ?{ INC } ( 0a )

Jump Immediate

JMI -- Moves the PC to a relative address at a distance equal to the next short in memory. This opcode has no modes, it is written using the !label format.

#0a !label INC @label ( 0a )

#0a !{ INC } ( 0a )

Jump Stash Return Immediate

JSI -- Pushes PC+2 to the return-stack and moves the PC to a relative address at a distance equal to the next short in memory. A plain label name resolves to a JSI operation. This opcode has no modes.

#07 #04 modulo BRK ( 03 ) @modulo ( a mod -- res ) DIVk MUL SUB JMP2r

Literal

LIT -- a

Pushes the next bytes in memory, and moves the PC forward by the same number of bytes (i.e: 1 byte if short mode is off or 2 bytes if it is on). The LIT opcode always has the keep mode active. Notice how the 0x00 opcode, with the keep bit toggled, is the location of the literal opcodes.

LIT 12 ( 12 ) LIT2 abcd ( ab cd )

Increment

.png)

INC a -- a+1 Increments the value at the top of the stack, by 1.

#01 INC ( 02 ) #0001 INC2 ( 00 02 ) #0001 INC2k ( 00 01 00 02 )

Pop

.png)

POP a -- Removes the value at the top of the stack. POPk is the canonical NOP.

#1234 POP ( 12 ) #1234 POP2 ( ) #1234 POP2k ( 12 34 )

Nip

.png)

NIP a b -- b Removes the second value from the stack. This is practical to truncate a short into a byte.

#1234 NIP ( 34 ) #1234 #5678 NIP2 ( 56 78 ) #1234 #5678 NIP2k ( 12 34 56 78 56 78 )

Swap

.png)

SWP a b -- b a Exchanges the first and second values at the top of the stack.

#1234 SWP ( 34 12 ) #1234 SWPk ( 12 34 34 12 ) #1234 #5678 SWP2 ( 56 78 12 34 ) #1234 #5678 SWP2k ( 12 34 56 78 56 78 12 34 )

Rotate

.png)

ROT a b c -- b c a Rotates three values at the top of the stack, to the left, wrapping around.

#1234 #56 ROT ( 34 56 12 ) #1234 #56 ROTk ( 12 34 56 34 56 12 ) #1234 #5678 #9abc ROT2 ( 56 78 9a bc 12 34 ) #1234 #5678 #9abc ROT2k ( 12 34 56 78 9a bc 56 78 9a bc 12 34 )

Duplicate

.png)

DUP a -- a a Duplicates the value at the top of the stack.

#1234 DUP ( 12 34 34 ) #12 DUPk ( 12 12 12 ) #1234 DUP2 ( 12 34 12 34 )

Over

.png)

OVR a b -- a b a Duplicates the second value at the top of the stack.

#1234 OVR ( 12 34 12 ) #1234 OVRk ( 12 34 12 34 12 ) #1234 #5678 OVR2 ( 12 34 56 78 12 34 ) #1234 #5678 OVR2k ( 12 34 56 78 12 34 56 78 12 34 )

Equal

.png)

EQU a b -- bool8 Pushes 01 to the stack if the two values at the top of the stack are equal, 00 otherwise.

#1212 EQU ( 01 ) #1234 EQUk ( 12 34 00 ) #abcd #ef01 EQU2 ( 00 ) #abcd #abcd EQU2k ( ab cd ab cd 01 )

Not Equal

.png)

NEQ a b -- bool8 Pushes 01 to the stack if the two values at the top of the stack are not equal, 00 otherwise.

#1212 NEQ ( 00 ) #1234 NEQk ( 12 34 01 ) #abcd #ef01 NEQ2 ( 01 ) #abcd #abcd NEQ2k ( ab cd ab cd 00 )

Greater Than

.png)

GTH a b -- bool8 Pushes 01 to the stack if the second value at the top of the stack is greater than the value at the top of the stack, 00 otherwise.

#1234 GTH ( 00 ) #3412 GTHk ( 34 12 01 ) #3456 #1234 GTH2 ( 01 ) #1234 #3456 GTH2k ( 12 34 34 56 00 )

Lesser Than

.png)

LTH a b -- bool8 Pushes 01 to the stack if the second value at the top of the stack is lesser than the value at the top of the stack, 00 otherwise.

#0101 LTH ( 00 ) #0100 LTHk ( 01 00 00 ) #0001 #0000 LTH2 ( 00 ) #0001 #0000 LTH2k ( 00 01 00 00 00 )

Jump

.png)

JMP addr -- Moves the PC by a relative distance equal to the signed byte on the top of the stack, or to an absolute address in short mode.

,&skip-rel JMP BRK &skip-rel #01 ( 01 )

Jump Conditional

.png)

JCN cond8 addr -- If the byte preceeding the address is not 00, moves the PC by a signed value equal to the byte on the top of the stack, or to an absolute address in short mode.

#abcd #01 ,&pass JCN SWP &pass POP ( ab ) #abcd #00 ,&fail JCN SWP &fail POP ( cd )

Jump Stash Return

.png)

JSR addr -- | ret16 Pushes the PC to the return-stack and moves the PC by a signed value equal to the byte on the top of the stack, or to an absolute address in short mode.

,&routine JSR ( | PC* ) ,&get JSR #01 BRK &get #02 JMP2r ( 02 01 )

Stash

.png)

STH a -- | a Moves the value at the top of the stack to the return stack. Note that with the r-mode, the stacks are exchanged and the value is moved from the return stack to the working stack.

#12 STH ( | 12 ) LITr 34 STHr ( 34 )

Load Zero-Page

LDZ addr8 -- value Pushes the value at an address within the first 256 bytes of memory, to the top of the stack.

|00 @cell $2 |0100 .cell LDZ ( 00 )

Store Zero-Page

STZ val addr8 -- Writes a value to an address within the first 256 bytes of memory.

|00 @cell $2 |0100 #abcd .cell STZ2 { ab cd }

Load Relative

LDR addr8 -- value Pushes a value at a relative address in relation to the PC, within a range between -128 and +127 bytes, to the top of the stack.

,cell LDR2 BRK @cell abcd ( ab cd )

Store Relative

STR val addr8 -- Writes a value to a relative address in relation to the PC, within a range between -128 and +127 bytes.

#1234 ,cell STR2 BRK @cell $2 ( )

Load Absolute

LDA addr16 -- value Pushes the value at a absolute address, to the top of the stack.

;cell LDA BRK @cell abcd ( ab )

Store Absolute

STA val addr16 -- Writes a value to a absolute address.

#abcd ;cell STA BRK @cell $1 ( ab )

Device Input

DEI device8 -- value Pushes a value from the device page, to the top of the stack. The target device might capture the reading to trigger an I/O event.

Device Output

DEO val device8 -- Writes a value to the device page. The target device might capture the writing to trigger an I/O event.

Add

.png)

ADD a b -- a+b Pushes the sum of the two values at the top of the stack.

#1a #2e ADD ( 48 ) #02 #5d ADDk ( 02 5d 5f ) #0001 #0002 ADD2 ( 00 03 )

Subtract

.png)

SUB a b -- a-b Pushes the difference of the first value minus the second, to the top of the stack.

#08 #03 SUB ( 05 ) #08 #02 SUBk ( 08 02 06 ) #2000 #1000 SUB2 ( 10 00 )

Multiply

.png)

MUL a b -- a*b Pushes the product of the first and second values at the top of the stack.

#06 #02 MUL ( 0c ) #08 #02 MULk ( 08 02 10 ) #0800 #0002 MUL2 ( 10 00 )

Divide

.png)

DIV a b -- a/b Pushes the quotient of the first value over the second, to the top of the stack. A division by zero pushes zero on the stack. The rounding direction is toward zero.

#10 #02 DIV ( 08 ) #10 #03 DIVk ( 10 03 05 ) #0010 #0000 DIV2 ( 00 00 )

And

.png)

AND a b -- a&b Pushes the result of the bitwise operation AND, to the top of the stack.

#fc #3f AND ( 3c )

Or

.png)

ORA a b -- a|b Pushes the result of the bitwise operation OR, to the top of the stack.

#fc #3f ORA ( ff )

Exclusive Or

.png)

EOR a b -- a^b Pushes the result of the bitwise operation XOR, to the top of the stack.

#fc #3f EOR ( c3 )

Shift

.png)

SFT a shift8 -- c Shifts the bits of the second value of the stack to the left or right, depending on the control value at the top of the stack. The high nibble of the control value indicates how many bits to shift left, and the low nibble how many bits to shift right. The rightward shift is done first.

#34 #10 SFT ( 68 ) #34 #01 SFT ( 1a ) #34 #33 SFTk ( 34 33 30 ) #1248 #34 SFTk2 ( 12 48 34 09 20 )

Using and operating on negative numbers in Uxntal.

Uxn doesn't have built-in support for negative integers. However, you can emulate signed numbers by treating some unsigned values as negative. For example, treating unsigned bytes as signed results in the following:

| hex | 00 | 01 | 02 | 7e | 7f | 80 | 81 | 82 | fd | fe | ff | ||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| unsigned | 0 | 1 | 2 | 126 | 127 | 128 | 129 | 130 | 253 | 254 | 255 | ||

| signed | 0 | 1 | 2 | 126 | 127 | -128 | -127 | -126 | -3 | -2 | -1 |

The first 128 integers (0-127) are represented the same as unsigned and signed, but the latter 128 are different. The basic idea here is that for values greater than #7f (127) we subtract 256 to get their signed value:

signed = n < 128 ? n : n - 256

It turns out that many unsigned operations "work" even when treating the values as signed. (In other words, you get the same result as you would have using a language with signed integer types.) The following arithmetic instructions work correctly with "signed" values:

#13 #ff ADD returns #12 #02 #03 SUB returns #ff #02 #ff MUL returns #fe

Be careful! The smallest negative value (-128 for bytes, -32768 for shorts) has no corresponding positive value. This means that some operations will not work as expected:

#80 #ff MUL returns #80 (-128 * -1 = -128) #00 #80 SUB returns #80 (0 - (-128) = -128)

Also, negative and positive values will "wrap around" in the usual way when dealing with two's-complement representations:

#7f #01 ADD returns #80 (127 + 1 = -128) #80 #01 SUB returns #7f (-128 - 1 = 127) #80 #80 ADD returns #00 (-128 + (-128) = 0)

Other instructions will not handle "negative" integers correctly. These routines will safely compare "signed" bytes:

@signed-lth ( x y -- res ) DUP2 #8080 AND2 EQU ?&diff LTH JMP2r &diff LTH #00 NEQ JMP2r @signed-gth ( x y -- res ) DUP2 #8080 AND2 EQU ?&diff GTH JMP2r &diff GTH #00 NEQ JMP2r

Similarly, division will not correctly handle signed values. The simplest way to handle this is to make both values non-negative, do unsigned division (i.e. DIV) and then set the correct sign at the end.

@abs ( x -- abs-x sign ) DUP #7f GTH #fe MUL INC STHk MUL STHr JMP2r @signed-div ( x y -- x/y ) abs STH SWP abs STH SWP DIV MULr STHr MUL JMP2r

The unsigned shift operator treats the sign bit like any other. This means shifting left will lose the sign bit (reversing the sign) and that shifting right will convert the sign bit into a value bit. Signed numbers will also need their own routines for decimal input and output, if those are required by your program.

@signed-print ( num -- )

( - ) DUP #80 LTH ?{ LIT "- #18 DEO #7f AND #80 SWP SUB }

( 100 ) DUP #64 DIV signed-print/emit

( 10 ) DUP #0a DIV signed-print/base

&base ( digit -- ) #0a DIVk MUL SUB

&emit ( digit -- ) LIT "0 ADD #18 DEO JMP2r

If you need a sign-aware shift you'll likely want to convert negatives to positive values, perform a shift, and then restore the sign. Keep in mind that -128 cannot be converted to a positive value, and may require special treatment.

Permutation table for the uxntal stack opcodes.

The stack assumes the elements a b c.

| POP POP | a |

| POP POP DUP | a a |

| POP POP DUPk | a a a |

| POP OVR SWP | a a b |

| NIP OVR SWP | a a c |

| POP | a b |

| POP OVR | a b a |

| POP OVR DUP | a b a a |

| POP OVR DUPk | a b a a a |

| POP OVR SWPk | a b a a b |

| POP OVR OVR | a b a b |

| POP OVRk | a b a b a |

| POP OVR ROTk | a b a b a a |

| POP OVRk DUPk | a b a b a a a |

| POP OVRk SWPk | a b a b a a b |

| POP OVR OVRk | a b a b a b |

| POP OVRk ROTk | a b a b a b a a |

| POP OVRk OVRk | a b a b a b a b |

| POP DUP | a b b |

| POP SWPk | a b b a |

| POP SWPk DUP | a b b a a |

| POP SWPk DUPk | a b b a a a |

| POP SWPk SWPk | a b b a a b |

| POP SWPk OVR | a b b a b |

| POP SWPk OVRk | a b b a b a b |

| ROTk NIP ROT | a b b a c |

| POP DUPk | a b b b |

| POP DUP DUPk | a b b b b |

| POP DUP ROTk | a b b b b a |

| POP DUP OVRk | a b b b b b |

| POP DUPk OVRk | a b b b b b b |

| OVR DUP ROT | a b b b c |

| OVR SWP | a b b c |

| OVR SWP OVR | a b b c b |

| OVR SWP OVRk | a b b c b c b |

| OVR SWP DUP | a b b c c |

| OVR SWP SWPk | a b b c c b |

| OVR SWP DUPk | a b b c c c |

| POPk | a b c |

| ROTk NIP NIP | a b c a |

| ROTk NIP SWP | a b c a b |

| ROTk ROT ROT | a b c a b c |

| ROTk SWP ROT | a b c a c b |

| OVR | a b c b |

| ROTk NIP | a b c b a |

| ROTk NIP DUP | a b c b a a |

| ROTk NIP DUPk | a b c b a a a |

| ROTk NIP SWPk | a b c b a a b |

| ROTk DUP ROT | a b c b a a c |

| ROTk NIP OVR | a b c b a b |

| ROTk NIP OVRk | a b c b a b a b |

| ROTk NIP ROTk | a b c b a b a c |

| ROTk SWP | a b c b a c |

| ROTk SWP OVR | a b c b a c a |

| ROTk SWP OVRk | a b c b a c a c a |

| ROTk SWP ROTk | a b c b a c a c b |

| ROTk SWP DUP | a b c b a c c |

| ROTk SWP SWPk | a b c b a c c a |

| ROTk SWP DUPk | a b c b a c c c |

| OVR DUP | a b c b b |

| OVR DUPk | a b c b b b |

| OVR DUP DUPk | a b c b b b b |

| OVR DUP OVRk | a b c b b b b b |

| OVR DUPk OVRk | a b c b b b b b b |

| OVR DUP ROTk | a b c b b b b c |

| OVR ROTk ROT | a b c b b b c |

| OVR SWPk | a b c b b c |

| OVR SWPk OVR | a b c b b c b |

| OVR SWPk OVRk | a b c b b c b c b |

| OVR SWPk DUP | a b c b b c c |

| OVR SWPk SWPk | a b c b b c c b |

| OVR SWPk DUPk | a b c b b c c c |

| OVR OVR | a b c b c |

| ROTk | a b c b c a |

| ROTk DUP | a b c b c a a |

| ROTk DUPk | a b c b c a a a |

| ROTk DUP DUPk | a b c b c a a a a |

| ROTk DUP OVRk | a b c b c a a a a a |

| ROTk DUPk OVRk | a b c b c a a a a a a |

| ROTk DUP ROTk | a b c b c a a a a c |

| ROTk ROTk ROT | a b c b c a a b c |

| ROTk SWPk | a b c b c a a c |

| ROTk SWPk OVR | a b c b c a a c a |

| ROTk SWPk OVRk | a b c b c a a c a c a |

| ROTk SWPk DUP | a b c b c a a c c |

| ROTk SWPk SWPk | a b c b c a a c c a |

| ROTk SWPk DUPk | a b c b c a a c c c |

| ROTk OVR | a b c b c a c |

| ROTk OVR OVR | a b c b c a c a |

| ROTk ROTk | a b c b c a c a b |

| ROTk ROTk OVR | a b c b c a c a b a |

| ROTk ROTk OVRk | a b c b c a c a b a b a |

| ROTk ROTk ROTk | a b c b c a c a b a b c |

| ROTk ROTk DUP | a b c b c a c a b b |

| ROTk ROTk SWPk | a b c b c a c a b b a |

| ROTk ROTk DUPk | a b c b c a c a b b b |

| ROTk OVRk | a b c b c a c a c |

| ROTk OVR OVRk | a b c b c a c a c a |

| ROTk OVRk OVRk | a b c b c a c a c a c a |

| ROTk OVRk ROTk | a b c b c a c a c a c c |

| ROTk OVR ROTk | a b c b c a c a c c |

| ROTk OVRk SWPk | a b c b c a c a c c a |

| ROTk OVRk DUPk | a b c b c a c a c c c |

| ROTk ROTk NIP | a b c b c a c b |

| ROTk ROTk SWP | a b c b c a c b a |

| ROTk OVR DUP | a b c b c a c c |

| ROTk OVR SWPk | a b c b c a c c a |

| ROTk OVR DUPk | a b c b c a c c c |

| OVRk | a b c b c b |

| OVR ROTk | a b c b c b b |

| OVRk DUPk | a b c b c b b b |

| OVR ROTk DUPk | a b c b c b b b b |

| OVR ROTk OVRk | a b c b c b b b b b |

| OVRk DUPk OVRk | a b c b c b b b b b b |

| OVR ROTk ROTk | a b c b c b b b b c |

| OVRk ROTk ROT | a b c b c b b b c |

| OVRk SWPk | a b c b c b b c |

| OVRk SWPk OVR | a b c b c b b c b |

| OVRk SWPk OVRk | a b c b c b b c b c b |

| OVRk SWPk DUP | a b c b c b b c c |

| OVRk SWPk SWPk | a b c b c b b c c b |

| OVRk SWPk DUPk | a b c b c b b c c c |

| OVR OVRk | a b c b c b c |

| OVR OVR OVRk | a b c b c b c b |

| OVRk ROTk | a b c b c b c b b |

| OVRk ROTk DUP | a b c b c b c b b b |

| OVRk ROTk DUPk | a b c b c b c b b b b |

| OVRk ROTk OVRk | a b c b c b c b b b b b |

| OVRk ROTk ROTk | a b c b c b c b b b b c |

| OVRk OVRk | a b c b c b c b c |

| OVR OVRk OVRk | a b c b c b c b c b |

| OVRk OVRk OVRk | a b c b c b c b c b c b |

| OVRk OVRk ROTk | a b c b c b c b c b c c |

| OVR OVRk ROTk | a b c b c b c b c c |

| OVRk OVRk SWPk | a b c b c b c b c c b |

| OVRk OVRk DUPk | a b c b c b c b c c c |

| OVR OVR ROTk | a b c b c b c c |

| OVR OVRk SWPk | a b c b c b c c b |

| OVR OVRk DUPk | a b c b c b c c c |

| OVR OVR DUP | a b c b c c |

| ROTk OVR SWP | a b c b c c a |

| OVR OVR SWPk | a b c b c c b |

| OVR OVR DUPk | a b c b c c c |

| DUP | a b c c |

| ROTk ROT POP | a b c c a |

| ROTk ROT | a b c c a b |

| ROTk ROT OVR | a b c c a b a |

| ROTk ROT OVRk | a b c c a b a b a |

| ROTk ROT ROTk | a b c c a b a b c |

| ROTk ROT DUP | a b c c a b b |

| ROTk ROT SWPk | a b c c a b b a |

| ROTk ROT DUPk | a b c c a b b b |

| SWPk | a b c c b |

| ROTk ROT SWP | a b c c b a |

| SWPk DUP | a b c c b b |

| SWPk DUPk | a b c c b b b |

| SWPk DUP DUPk | a b c c b b b b |

| SWPk DUP OVRk | a b c c b b b b b |

| SWPk DUPk OVRk | a b c c b b b b b b |

| SWPk DUP ROTk | a b c c b b b b c |

| SWPk SWPk | a b c c b b c |

| SWPk SWPk OVR | a b c c b b c b |

| SWPk SWPk OVRk | a b c c b b c b c b |

| SWPk SWPk DUP | a b c c b b c c |

| SWPk SWPk SWPk | a b c c b b c c b |

| SWPk SWPk DUPk | a b c c b b c c c |

| SWPk OVR | a b c c b c |

| SWPk OVR OVR | a b c c b c b |

| SWPk OVRk | a b c c b c b c |

| SWPk OVR OVRk | a b c c b c b c b |

| SWPk OVRk OVRk | a b c c b c b c b c b |

| SWPk OVRk ROTk | a b c c b c b c b c c |

| SWPk OVR ROTk | a b c c b c b c c |

| SWPk OVRk SWPk | a b c c b c b c c b |

| SWPk OVRk DUPk | a b c c b c b c c c |

| SWPk OVR DUP | a b c c b c c |

| SWPk OVR SWPk | a b c c b c c b |

| SWPk OVR DUPk | a b c c b c c c |

| DUPk | a b c c c |

| DUP ROTk NIP | a b c c c b |

| DUP ROTk SWP | a b c c c b c |

| DUP DUPk | a b c c c c |

| DUP ROTk | a b c c c c b |

| DUP ROTk DUP | a b c c c c b b |

| DUP ROTk DUPk | a b c c c c b b b |

| DUP ROTk SWPk | a b c c c c b b c |

| DUP ROTk OVR | a b c c c c b c |

| DUP ROTk OVRk | a b c c c c b c b c |

| DUP OVRk | a b c c c c c |

| DUPk OVRk | a b c c c c c c |

| DUP DUPk OVRk | a b c c c c c c c |

| DUP OVRk OVRk | a b c c c c c c c c |

| DUPk OVRk OVRk | a b c c c c c c c c c |

| NIP | a c |

| NIP OVR | a c a |

| NIP OVR DUP | a c a a |

| NIP OVR DUPk | a c a a a |

| NIP OVR SWPk | a c a a c |

| NIP OVR OVR | a c a c |

| NIP OVRk | a c a c a |

| NIP OVR ROTk | a c a c a a |

| NIP OVRk DUPk | a c a c a a a |

| NIP OVRk SWPk | a c a c a a c |

| NIP OVR OVRk | a c a c a c |

| NIP OVRk ROTk | a c a c a c a a |

| NIP OVRk OVRk | a c a c a c a c |

| SWP | a c b |

| SWP DUP | a c b b |

| SWP ROTk ROT | a c b b a c |

| SWP DUPk | a c b b b |

| SWP DUP DUPk | a c b b b b |

| SWP DUP OVRk | a c b b b b b |

| SWP DUPk OVRk | a c b b b b b b |

| SWP DUP ROTk | a c b b b b c |

| SWP SWPk | a c b b c |

| SWP SWPk OVR | a c b b c b |

| SWP SWPk OVRk | a c b b c b c b |

| SWP SWPk DUP | a c b b c c |

| SWP SWPk SWPk | a c b b c c b |

| SWP SWPk DUPk | a c b b c c c |

| SWP OVR | a c b c |

| SWP ROTk NIP | a c b c a |

| SWP ROTk SWP | a c b c a b |

| SWP OVR OVR | a c b c b |

| SWP ROTk | a c b c b a |

| SWP ROTk DUP | a c b c b a a |

| SWP ROTk DUPk | a c b c b a a a |

| SWP ROTk SWPk | a c b c b a a b |

| SWP ROTk OVR | a c b c b a b |

| SWP ROTk OVRk | a c b c b a b a b |

| SWP ROTk ROTk | a c b c b a b a c |

| SWP OVRk | a c b c b c |

| SWP OVR OVRk | a c b c b c b |

| SWP OVRk OVRk | a c b c b c b c b |

| SWP OVRk ROTk | a c b c b c b c c |

| SWP OVR ROTk | a c b c b c c |

| SWP OVRk SWPk | a c b c b c c b |

| SWP OVRk DUPk | a c b c b c c c |

| SWP OVR DUP | a c b c c |

| SWP OVR SWPk | a c b c c b |

| SWP OVR DUPk | a c b c c c |

| NIP DUP | a c c |

| NIP SWPk | a c c a |

| NIP SWPk DUP | a c c a a |

| NIP SWPk DUPk | a c c a a a |

| NIP SWPk SWPk | a c c a a c |

| NIP SWPk OVR | a c c a c |

| NIP SWPk OVRk | a c c a c a c |

| DUP ROT | a c c b |

| DUP ROT DUP | a c c b b |

| DUP ROT DUPk | a c c b b b |

| DUP ROT SWPk | a c c b b c |

| DUP ROT OVR | a c c b c |

| DUP ROT OVRk | a c c b c b c |

| NIP DUPk | a c c c |

| NIP DUP DUPk | a c c c c |

| NIP DUP ROTk | a c c c c a |

| NIP DUP OVRk | a c c c c c |

| NIP DUPk OVRk | a c c c c c c |

| POP NIP | b |

| POP SWP | b a |

| POP SWP DUP | b a a |

| POP SWP DUPk | b a a a |

| POP SWP SWPk | b a a b |

| ROT DUP ROT | b a a c |

| POP SWP OVR | b a b |

| POP SWP OVRk | b a b a b |

| ROT SWP | b a c |

| ROT SWP OVR | b a c a |

| ROT SWP OVRk | b a c a c a |

| ROT SWP ROTk | b a c a c b |

| ROT SWP DUP | b a c c |

| ROT SWP SWPk | b a c c a |

| ROT SWP DUPk | b a c c c |

| POP NIP DUP | b b |

| POP DUP ROT | b b a |

| POP NIP DUPk | b b b |

| ROT POP | b c |

| ROT | b c a |

| ROT DUP | b c a a |

| ROT DUPk | b c a a a |

| ROT DUP DUPk | b c a a a a |

| ROT DUP OVRk | b c a a a a a |

| ROT DUPk OVRk | b c a a a a a a |

| ROT DUP ROTk | b c a a a a c |

| ROT ROTk ROT | b c a a b c |

| ROT SWPk | b c a a c |

| ROT SWPk OVR | b c a a c a |

| ROT SWPk OVRk | b c a a c a c a |

| ROT SWPk DUP | b c a a c c |

| ROT SWPk SWPk | b c a a c c a |

| ROT SWPk DUPk | b c a a c c c |

| ROT OVR | b c a c |

| ROT OVR OVR | b c a c a |

| ROT ROTk | b c a c a b |

| ROT ROTk OVR | b c a c a b a |

| ROT ROTk OVRk | b c a c a b a b a |

| ROT ROTk ROTk | b c a c a b a b c |

| ROT ROTk DUP | b c a c a b b |

| ROT ROTk SWPk | b c a c a b b a |

| ROT ROTk DUPk | b c a c a b b b |

| ROT OVRk | b c a c a c |

| ROT OVR OVRk | b c a c a c a |

| ROT OVRk OVRk | b c a c a c a c a |

| ROT OVRk ROTk | b c a c a c a c c |

| ROT OVR ROTk | b c a c a c c |

| ROT OVRk SWPk | b c a c a c c a |

| ROT OVRk DUPk | b c a c a c c c |

| ROT ROTk NIP | b c a c b |

| ROT ROTk SWP | b c a c b a |

| ROT OVR DUP | b c a c c |

| ROT OVR SWPk | b c a c c a |

| ROT OVR DUPk | b c a c c c |

| ROT POP OVR | b c b |

| ROT POP OVRk | b c b c b |

| ROT POP DUP | b c c |

| ROT OVR SWP | b c c a |

| ROT POP SWPk | b c c b |

| ROT POP DUPk | b c c c |

| NIP NIP | c |

| NIP SWP | c a |

| NIP SWP DUP | c a a |

| NIP SWP DUPk | c a a a |

| NIP SWP SWPk | c a a c |

| ROT ROT | c a b |

| ROT ROT OVR | c a b a |

| ROT ROT OVRk | c a b a b a |

| ROT ROT ROTk | c a b a b c |

| ROT ROT DUP | c a b b |

| ROT ROT SWPk | c a b b a |

| ROT ROT DUPk | c a b b b |

| NIP SWP OVR | c a c |

| NIP SWP OVRk | c a c a c |

| SWP ROT POP | c b |

| SWP ROT | c b a |

| SWP ROT DUP | c b a a |

| SWP ROT DUPk | c b a a a |

| SWP ROT SWPk | c b a a b |

| SWP ROT OVR | c b a b |

| SWP ROT OVRk | c b a b a b |

| SWP ROT ROTk | c b a b a c |

| NIP NIP DUP | c c |

| NIP DUP ROT | c c a |

| NIP NIP DUPk | c c c |